11

-

- Implementing digital systems

● Introduction

● Introduction

● Array logic

● FPGA

● VHDL

-

- Introduction

- Watch the Video 📹

● In this lecture we will look at the techniques used to implement complex digital systems

● We will begin by looking at the nature of various complex integrated circuits, and then progress to look at implementation strategies

● The complexity of the integrated circuits used within electronic circuits is increasing rapidly

● Available integration level increases exponentially with time (Moore’s Law) -

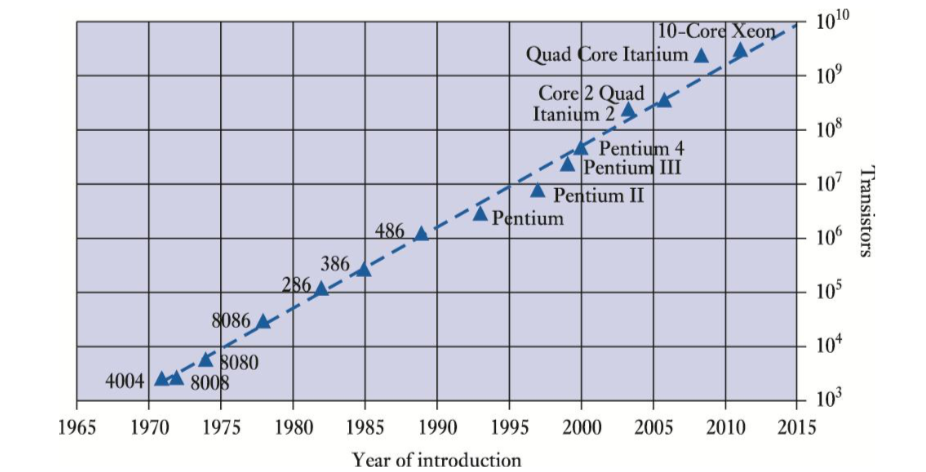

- Moore's Law

- ● Integration densities of Intel microprocessors

-

- Array logic

- ● Programmable logic devices (PLDs)

–these are examples of uncommitted logic

–forms include:

• programmable logic array (PLA)

• programmable array logic (PAL)

• generic array logic (GAL)

• erasable programmable logic device (EPLD)

• programmable electrically erasable logic (PEEL)

• programmable read only memory (PROM)

• complex programmable logic device (CPLD)

• field programmable gate array (FPGA)

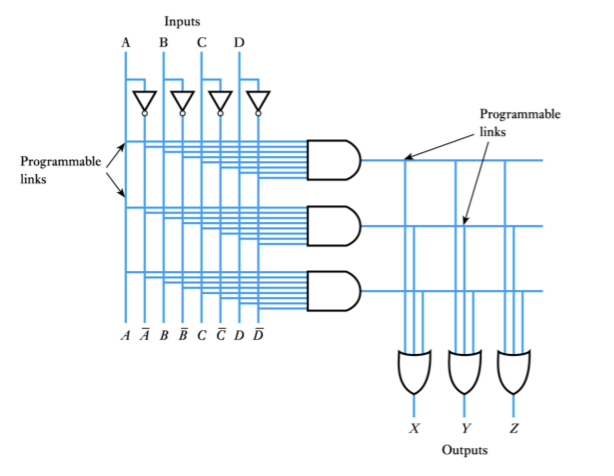

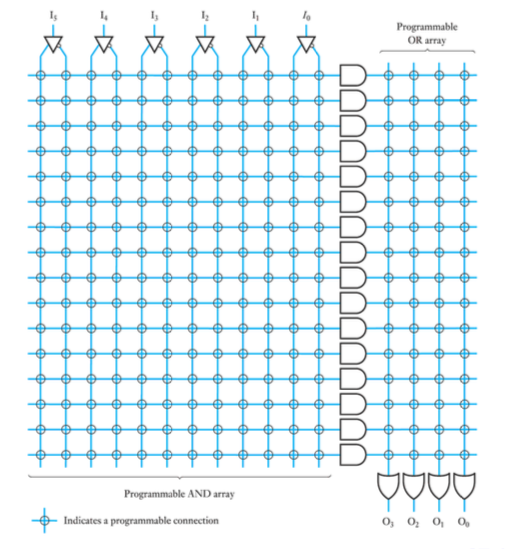

● Programmable logic array (PLA)

–has an array of inverters, AND gates and OR gates

–can implement any logic function (given limits on numbers of inputs and outputs)

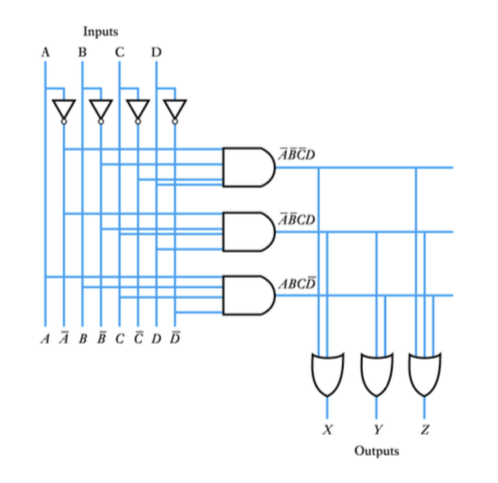

Example: consider a system with four inputs A, B, C and D and three output X, Y and Z, where

X=\overline{A}\,\overline{B}\,\overline{C}D + \overline{A}\,\overline{B}CD

Y=\overline{A}\,\overline{B}CD + ABC\overline{D}

Z=\overline{A}\,\overline{B}\,\overline{C}D + \overline{A}\,\overline{B}CD + ABC\overline{D}

–the structure of a simple PLA

–the PLA programmed to give the required output functions

–the device is programmed by blowing fusible links at the various interconnection points

–logic array symbolic notation

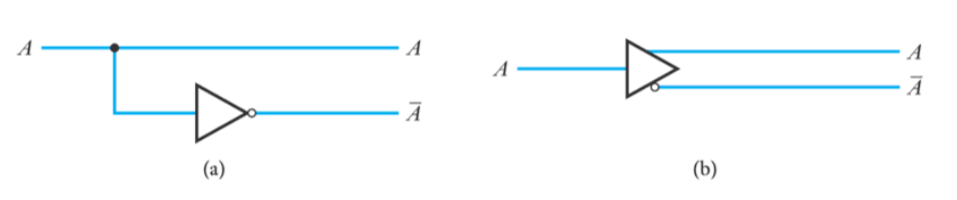

–representation of inverters within logic arrays

–a PLA with 6 inputs, 4 outputs and 16 product terms

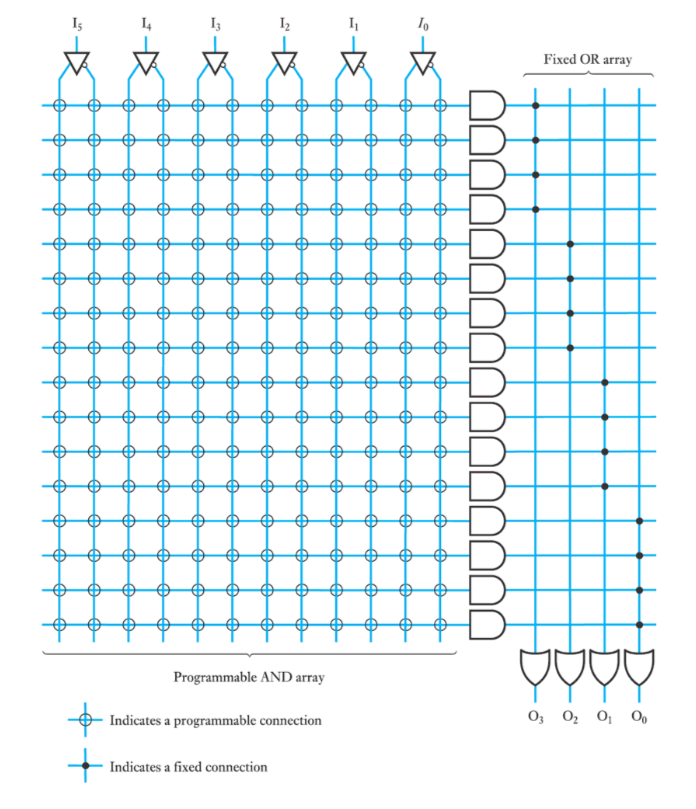

● Programmable array logic (PAL)

Watch the Video 📹

– similar structure to the PLA – but has only one programmable array

– the AND array is equivalent to that in a PLA

– the OR array is replaced by a fixed pattern of connections

– a range of devices is available with different numbers of OR gates and different numbers of inputs to each OR gate

– a PAL with 6 inputs, 4 outputs and 16 product terms

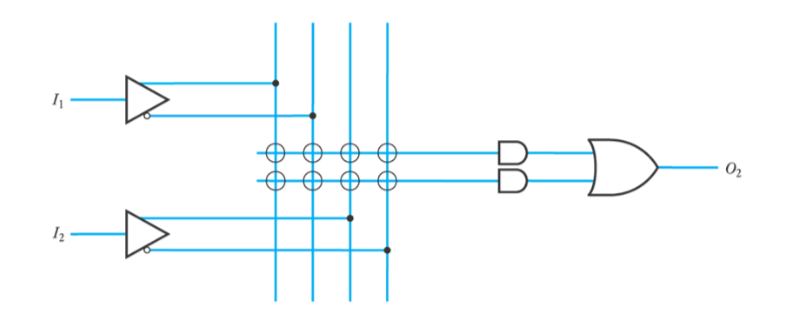

– since the OR array is fixed, it is common to omit it from the diagram, and to put the inputs on the left and the outputs on the right – as in the fragment shown below

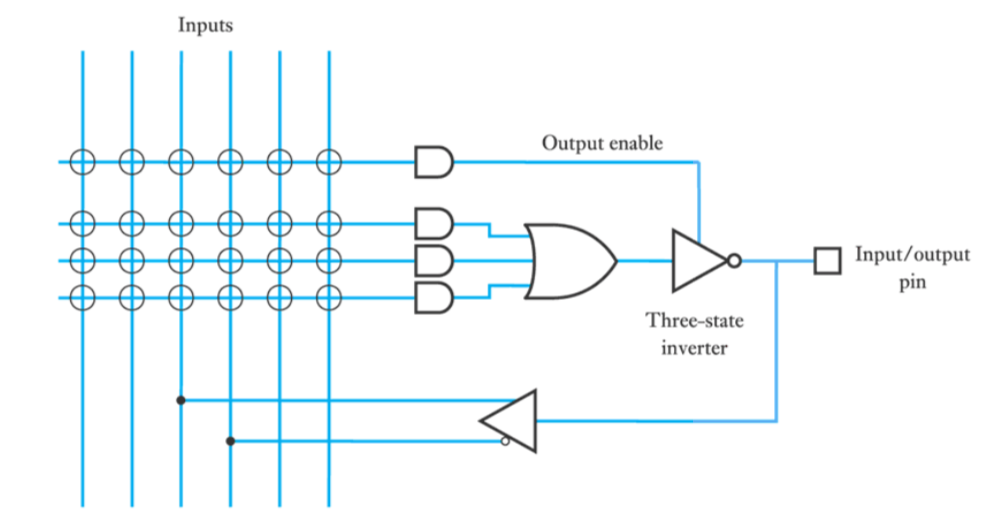

many PALs use a technique that allows their pins to be configured as inputs or output

–the output enable is derived from the input array and can be fixed (programmed) or determined by the inputs

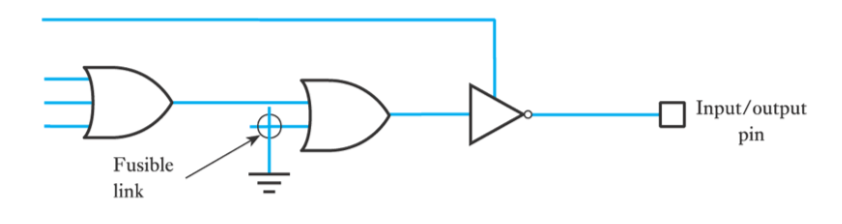

–some PALs have an Exclusive OR gate at their output

–one input to this gate is a fusible link to ground

–if this fuse is blown the output signal will be inverted

● GALs and EPLDs

–because of their use of fuses PALs can only be programmed once – they are one-time programmable (OTP)

–generic array logic (GAL) devices are pin compatible with PALs, but use electrically erasable (EEPROM) technology in place of fuses to provide reprogrammability

–erasable PLDs (EPLDs) are also reprogrammable, using EPROM techniques to allow them to be erased using UV light

● Programmable electrically erasable logic (PEEL)

– uses CMOS EEPROM techniques

– similar architecture to that of macrocell PALs, but use more sophisticated macrocell structure

– CMOS technology permits low power consumption

– devices are available for 5 V and 3 V operation

– low-power versions require only a few milliamps when operational and only a few microamps when in standby

● Programmable read-only memory (PROM)

– similar structure to a PLA but has only 1 programmable array (as in the PAL)

– however, here it is the OR array that is programmable

– each combination of inputs selects one AND gate and the OR array is used to determine, which of the outputs is taken high (logical 1) for that combination of inputs

– the pattern written into the OR array thus determines the outputs produced for each combination of inputs

– can be used to implement logic functions or to store data – when storing data the inputs are the address

-

- CPLD

Watch the Video 📹

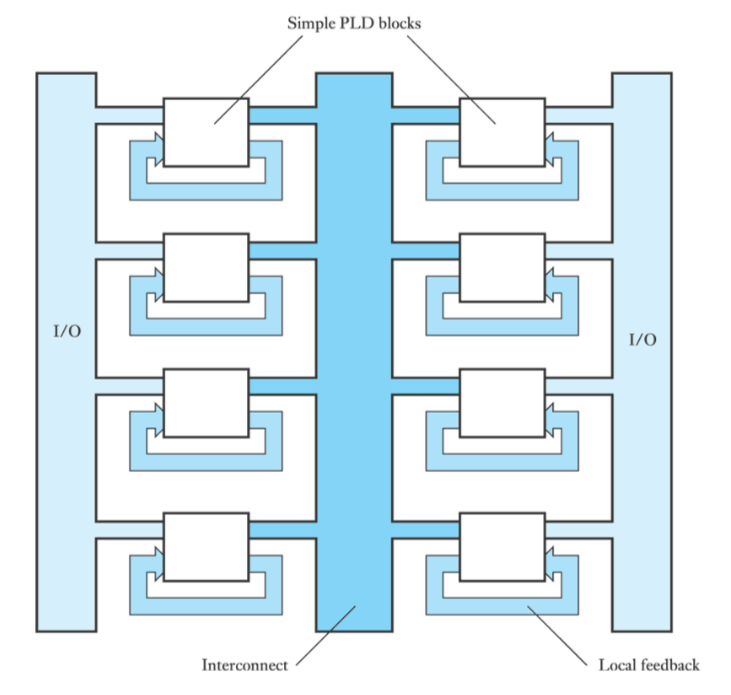

● Complex programmable logic device (CPLD)

– PLAs, PALs, GALs, EPLDs and PEELs are simple programmable logic devices (SPLDs)

– a CPLD is effectively several SPLDs on a single chip, with programmable interconnectivity

-

- FPGA

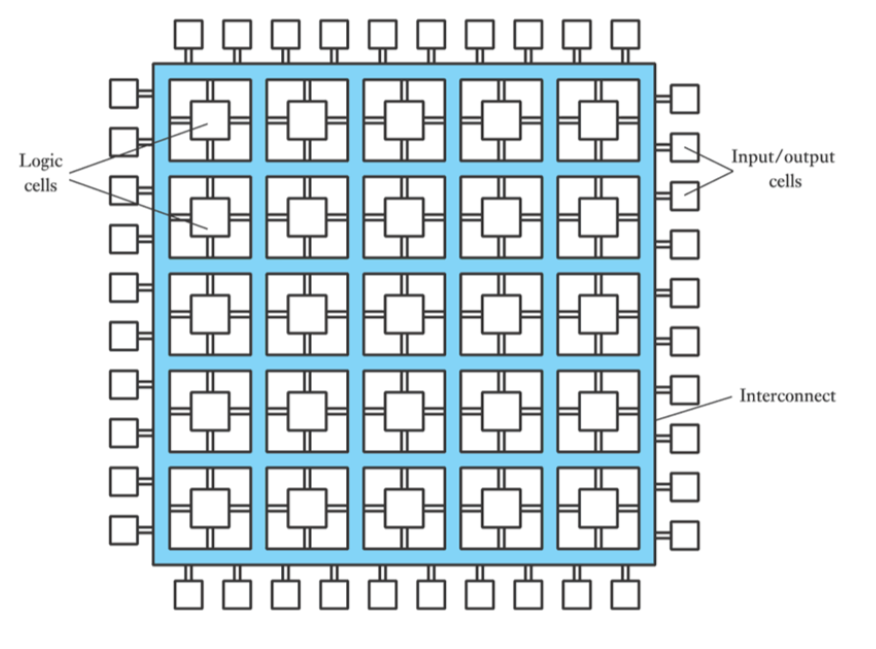

- ● Field programmable gate array (FPGA)

– a programmable device using more complex cells

– programmable switches are used to interconnect the various elements

– The cells in an FPGA vary tremendously from one manufacturer to another – might include registers, multiplexers and look-up tables

– More sophisticated devices include hardware multipliers, memory blocks, phase-lock loops and input/output buffers

– Programmable switches may be OTP (using antifuses) or reprogrammable

– Reprogrammable parts replace the fuse by a MOSFET switch which is controlled by a memory element – this is a static random access memory (SRAM) approach

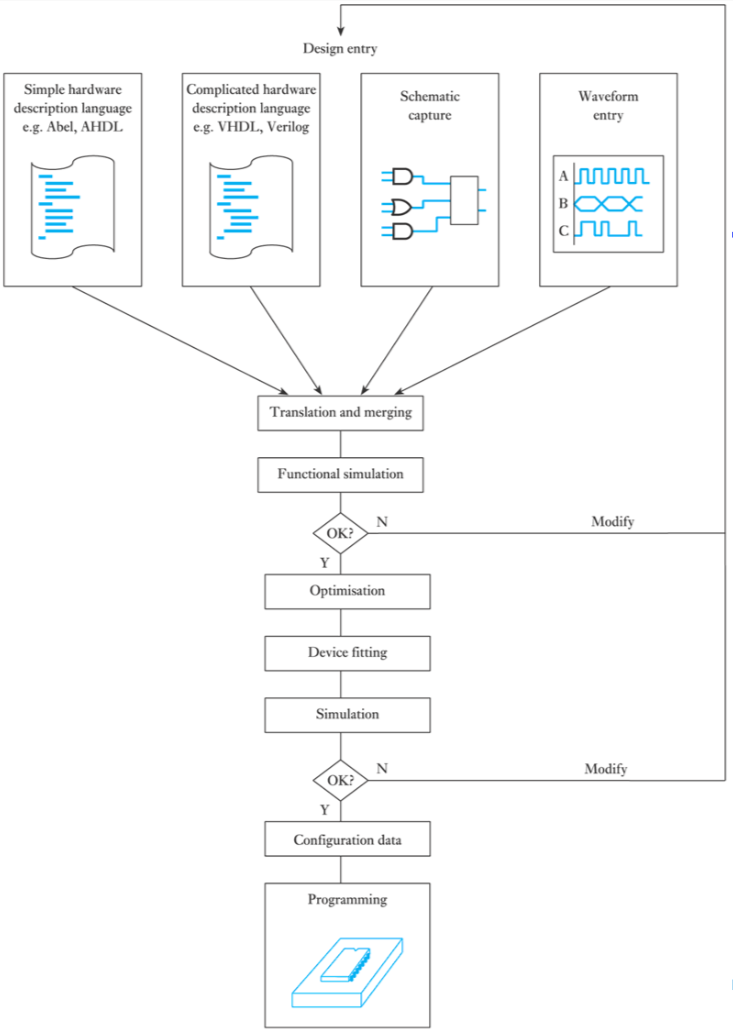

● Programming tools for array logic

– automated tools are used in almost all cases

– often make use of hardware description languages

– fuse maps are passed to a programmer to configure the device

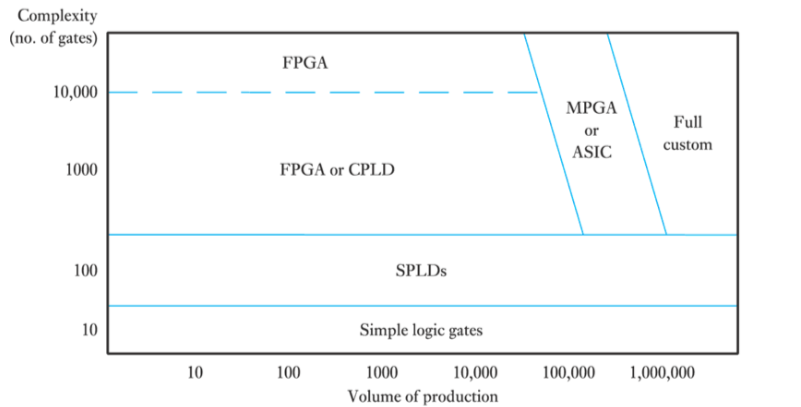

● Custom and semi-custom ICs

– when producing systems in large quantities it may be cost effective to produce a custom IC

– for more modest projects a semi-custom or application specific integrated circuit (ASIC) may be more appropriate

• produced by combining a number of standard cells (such as registers, counters, input/output circuitry and memory)

• much less costly than a complete design from scratch

• however, design tends to be less efficient that a full custom design, resulting in a larger and therefore more expensive chip

-

- Choosing between the various forms of implementation

- VHDL (used with FPGAs)

● Very-High-Speed-IC Hardware Description Language -

- Key points

- ● Available complexity doubles every couple of years

● Array logic integrates large numbers of gates within a single package that is then configured for a particular application

● Complex digital systems can also be implemented using a microcomputer

● A programmable logic controller is a self-contained microcomputer that is optimised for industrial control

● The implementation method used will depend on the complexity of the required system

-